What is Nano SOI?

Introduction

There are two options for accessing the NanoSOI fabrication process. Multi-project wafer (MPW) runs are scheduled once every two months. Standard processes and immediate pricing are available for these runs. Dedicated runs are for projects requiring custom options such as selective oxide release. Timelines for these runs are flexible, and quotations are customized for each run.

There are two options for accessing the NanoSOI fabrication process. Multi-project wafer (MPW) runs are scheduled once every two months. Standard processes and immediate pricing are available for these runs. Dedicated runs are for projects requiring custom options such as selective oxide release. Timelines for these runs are flexible, and quotations are customized for each run.

Submission Process

Submission of a design to the NanoSOI process is done online. Design files are provided to us in Calma Graphics Data System II (GDSII) format, with database units of 1 nanometre. Designs are submitted online using the NanoSOI Design Center, which can be accessed by choosing “Submit A Design” in the navigation bar above. The latest design rules, layout tutorials, and details about the fabrication process are all located at the NanoSOI Design Center. Pricing for multi-project wafer runs is also available online through the Design Center.

Fabrication Details

Our fabrication process, including all of our standard options, is outlined below. Jump to any process step using the sidebar on the right.

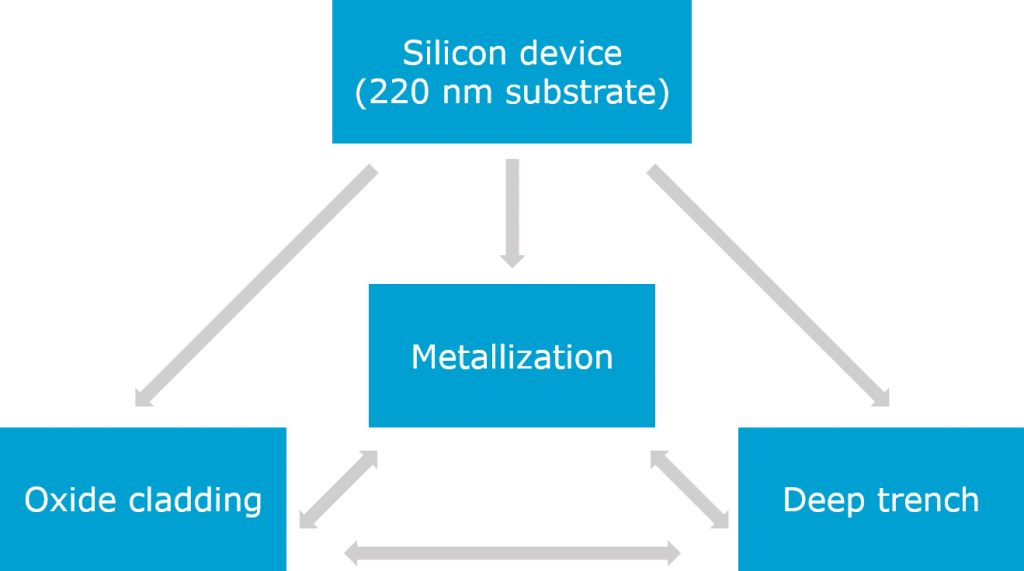

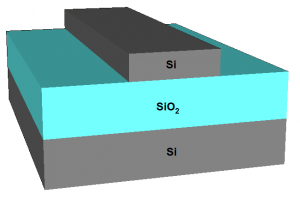

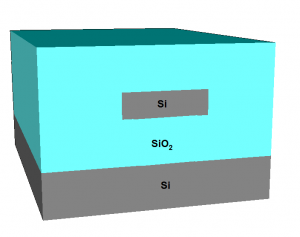

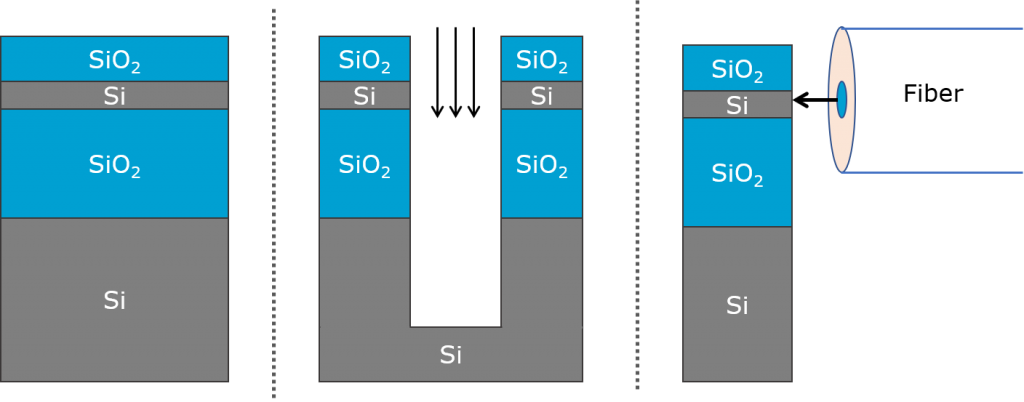

Silicon Device Layer

Our silicon patterning process involves the definition of nano-scale features in silicon-on-insulator (SOI) using electron beam lithography (EBL) and reactive ion etching (RIE) processes. The substrate is a 220 nm silicon device layer with a 2 µm buried oxide layer and 675 µm handle wafer. The patterning process begins by cleaning and spin-coating a material that is sensitive to electron beam exposure. A device pattern is defined into this material using 100 keV EBL. Once the material has been chemically developed, an anisotropic ICP-RIE etching process is performed on the substrate to transfer the pattern into the underlying silicon layer. The etch is performed until there is no remaining silicon and the underlying buffer oxide layer is exposed. Once the silicon patterning step has been completed, several standard options become available to add extra functionality to the device, including oxide deposition to protect and isolate silicon devices, metallization to give the devices electrical functionality, and deep trenches to provide a smooth interface for fiber edge-coupling. Custom options include selective oxide release to create free-standing silicon structures for mechanical applications.

Our silicon patterning process involves the definition of nano-scale features in silicon-on-insulator (SOI) using electron beam lithography (EBL) and reactive ion etching (RIE) processes. The substrate is a 220 nm silicon device layer with a 2 µm buried oxide layer and 675 µm handle wafer. The patterning process begins by cleaning and spin-coating a material that is sensitive to electron beam exposure. A device pattern is defined into this material using 100 keV EBL. Once the material has been chemically developed, an anisotropic ICP-RIE etching process is performed on the substrate to transfer the pattern into the underlying silicon layer. The etch is performed until there is no remaining silicon and the underlying buffer oxide layer is exposed. Once the silicon patterning step has been completed, several standard options become available to add extra functionality to the device, including oxide deposition to protect and isolate silicon devices, metallization to give the devices electrical functionality, and deep trenches to provide a smooth interface for fiber edge-coupling. Custom options include selective oxide release to create free-standing silicon structures for mechanical applications.

Waveguide Components

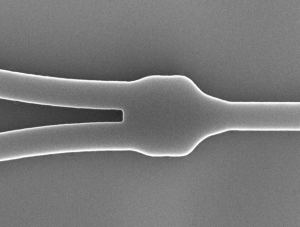

Y Splitter (50/50) on 220 nm SOI

Y Splitter (50/50) on 220 nm SOIGrating Couplers

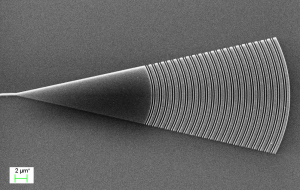

Sub-wavelength grating coupler patterned on 300 nm SOI

Sub-wavelength grating coupler patterned on 300 nm SOIPhotonics Crystals

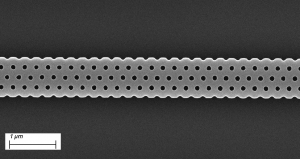

Photonic crystal strip waveguide patterned on 300 nm SOI

Photonic crystal strip waveguide patterned on 300 nm SOIPropagation Loss measurements

| Polarization | Straight Waveguide Loss | Curved Waveguide Loss |

|---|---|---|

| TE | 1.5 dB/cm | 3.8 dB/cm |

| TM | 2.4 dB/cm | 3.0 dB/cm |

These results are averaged over two sets of test arrays. Each set was separated by 9 mm. Detailed measurement data, including spectral scans, can be provided by request.

Oxide Deposition

If the silicon devices require isolation from the outside environment, silicon dioxide can be deposited onto the device using a chemical vapour deposition (CVD) process. Our standard oxide deposition thickness is is 2.2 µm, which is sufficient for most thermal and optical applications. The oxide deposition process can be combined with our tri-layer heater metallization process to fabricate active photonic devices that can be controlled with temperature. Custom oxide thicknesses up to 3 µm can be requested.

If the silicon devices require isolation from the outside environment, silicon dioxide can be deposited onto the device using a chemical vapour deposition (CVD) process. Our standard oxide deposition thickness is is 2.2 µm, which is sufficient for most thermal and optical applications. The oxide deposition process can be combined with our tri-layer heater metallization process to fabricate active photonic devices that can be controlled with temperature. Custom oxide thicknesses up to 3 µm can be requested.

Metalization

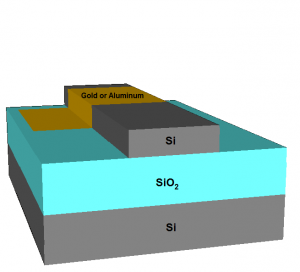

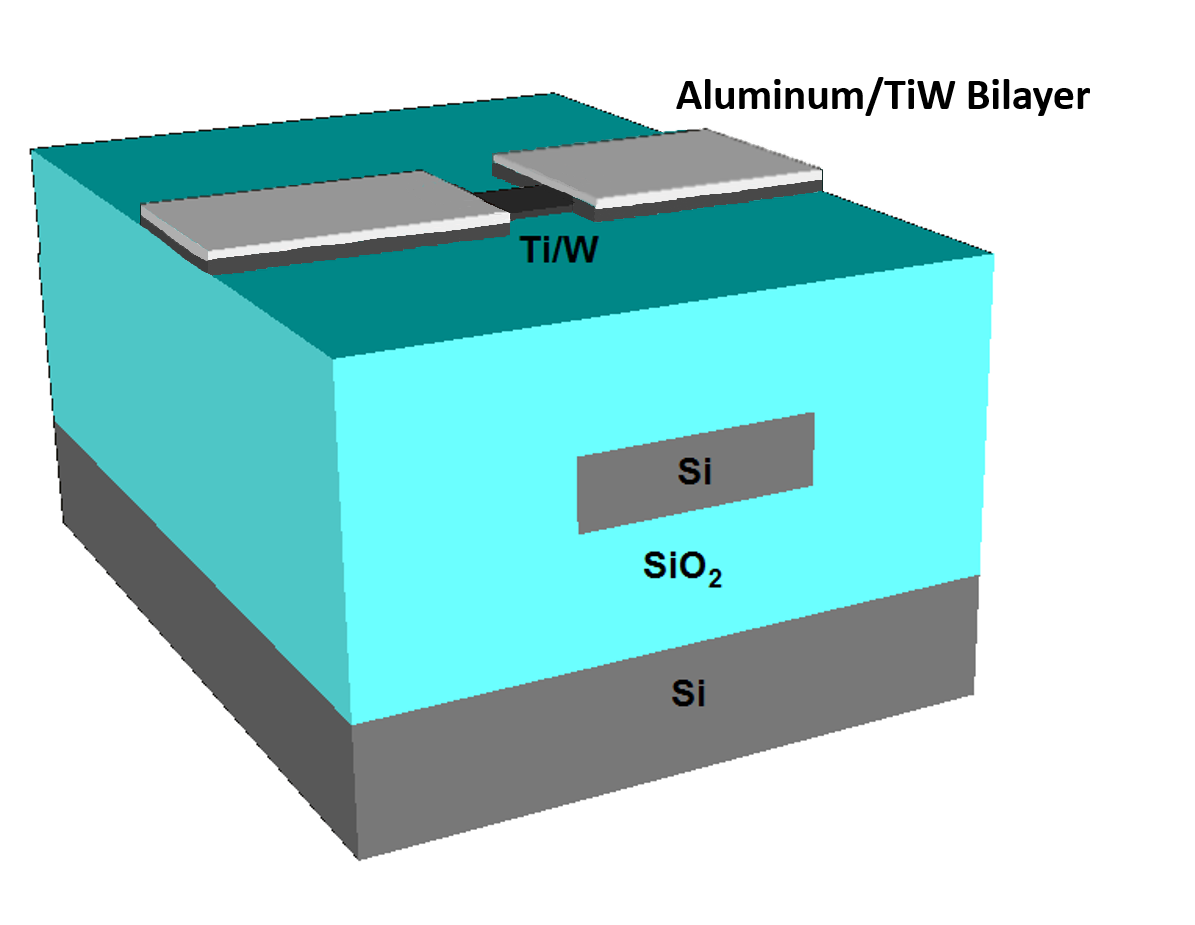

Metallization adds electrical functionality to your device. ANT has two metallization processes, which are either performed directly on the silicon features or on top of the oxide cladding (if deposited in the previous step). The former enables the direct application of a voltage/current to a silicon device, and the latter enables low-loss thermo-optic photonic devices.

Derect Metalization

| Metal | Thinkness |

|---|---|

| Gold (with 4 nm Cr adhesion layer) | 100 nm |

Tri-layer metalization

* Protective oxide layer not shown.

* Protective oxide layer not shown.| Metal | Thinkness |

|---|---|

| TiW Alloy Heater Layer | Thickness: 200 nm Bulk Resistivity: 0.61 μΩ-m Sheet Resistance: 3.07 Ω/sq |

| TTiW/Al Bilayer Routing Layer | Thickness: 200 nm Ti/W + 500 nm Al Bulk Resistivity: 0.04 μΩ-m Sheet Resistance: 0.08 Ω/sq |

| Silicon Dioxide Protective Layer | Thickness: 300 nm Bulk Resistivity: N/A Sheet Resistance: N/A |

Deep Trench Etch

SOI芯片订制

SOI芯片订制